# Interfacing DDR2 SDRAM with Stratix II, Stratix II GX, and Arria GX Devices

November 2007, ver. 4.0 Application Note 328

#### Introduction

DDR2 SDRAM is the second generation of double-data rate (DDR) SDRAM technology, with features such as lower power consumption, higher data bandwidth, enhanced signal quality, and on-die termination schemes. DDR2 SDRAM brings higher memory performance to a broad range of applications, such as PCs, embedded processor systems, image processing, storage, communications, and networking.

Stratix<sup>®</sup> II and Stratix II GX devices support two modes of DDR2 SDRAM interfacing: with and without dedicated DQS phase-shift circuitry. In addition, Stratix II and Stratix II GX device families offer two different data paths or physical interfaces (PHYs) with the dedicated DQS phase-shift circuitry: the legacy integrated static data path and controller (referred to as the legacy controller in this document) and ALTMEMPHY.

Table 1 displays the maximum clock frequency for DDR2 SDRAM interfaces in Stratix II and Stratix II GX devices with and without using dedicated DQS phase-shift circuitry.

| Table 1. DDR2 SDRAM Interface Maximum Clock Frequency Support in Stratix II and Stratix II GX Dev | ices |

|---------------------------------------------------------------------------------------------------|------|

| Notes (1), (2), (3)                                                                               |      |

|       | Frequency (MHz) |                     |            |                                 |

|-------|-----------------|---------------------|------------|---------------------------------|

| Speed | Wit             | h Dedicated DQS Cir | cuitry     | Without Dedicated DQS Circuitry |

| Grade | ALTMEMPHY       |                     | Lagon DIIV | Largey BUV                      |

|       | Half-Rate Mode  | Full-Rate Mode      | Legacy PHY | Legacy PHY                      |

| -3    | 333             | 267                 | 267        | 200                             |

| -4    | 267             | 233                 | 267        | 167                             |

| -5    | 233             | 200                 | 233        | 167                             |

#### Notes for Table 1:

- (1) The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your design's actual achievable performance is based on design and system specific factors, as well as static timing analysis of the completed design.

- (2) These specifications apply to both commercial and industrial devices.

- (3) These specifications are applicable for both interfacing with DDR2 SDRAM modules and discrete devices.

The Arria™ GX device family supports only ALTMEMPHY-based memory interfaces with dedicated DQS phase-shift circuitry. Memory interfaces with ALTMEMPHY can use either half-rate mode where the system clock for the controller is half the frequency of the memory interface frequency or full-rate mode where the system clock and the memory interface frequencies are the same.

Table 2 displays the maximum clock frequency for DDR2 SDRAM interfaces in Arria GX devices.

| Table 2. DDR2 SDRAM Interface Maximum Clock Frequency Support in Arria GX Devices | Notes (1), (2), |

|-----------------------------------------------------------------------------------|-----------------|

| (3), (4)                                                                          |                 |

| Speed Grade | Frequency (MHz)     |     |  |  |

|-------------|---------------------|-----|--|--|

| Speed drade | Half-Rate Full-Rate |     |  |  |

| -6          | 233                 | 200 |  |  |

#### Notes for Table 2:

- (1) The supported operating frequencies listed here are memory interface maximums for the FPGA device family. Your design's actual achievable performance is based on design and system specific factors, as well as static timing analysis of the completed design.

- (2) These specifications apply to both commercial and industrial devices.

- (3) These specifications are applicable for both interfacing with DDR2 SDRAM modules and discrete devices.

- (4) DDR2 SDRAM memory interface support in Arria GX devices is only available with ALTMEMPHY implementation.

This application note describes Altera's® recommended design flow for implementing a DDR2 SDRAM memory interface on a Stratix II, Stratix II GX, or Arria GX FPGA. Two example design walk-throughs are provided that detail critical aspects of this flow, including:

- Instantiating the PHY to a DDR2 SDRAM device

- Setting appropriate constraints on the PHY

- Verifying design functionality using simulation

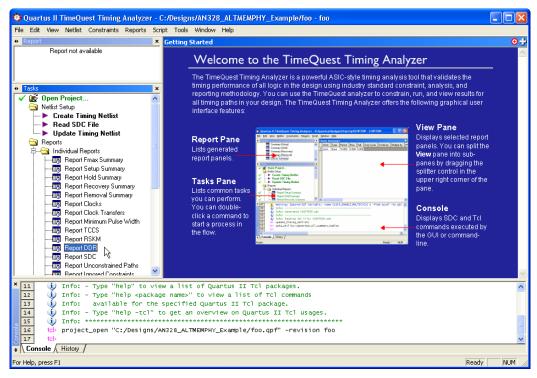

- Timing closure using the TimeQuest Timing Analyzer in the Quartus<sup>®</sup> II software.

This application note includes two example designs that interface with five DDR2 SDRAM devices (amounting to a 72-bit interface) available in the Stratix II GX PCI-Express Development Kit. One example design uses the ALTMEMPHY megafunction and the other example design uses the legacy PHY.

After un-archiving the example design, ensure that you point to the corresponding IP library in your Quartus II installation directory. The IP library is located in the <quartus\_install\_directory>\<version>\ip\ddr2\_high\_perf for the ALTMEMPHY-based controller and in the <quartus\_install\_directory>\<version>\ip\ddr\_ddr2\_sdram\ lib for the legacy controller.

#### **DDR2 SDRAM Overview**

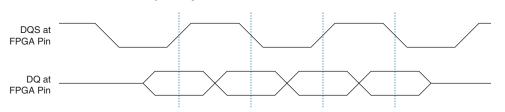

DDR2 SDRAM is the second generation of the DDR SDRAM memory standard. It is a 4*n* pre-fetch architecture with two data transfers per clock cycle. The memory uses a strobe (DQS) associated with a group of data pins (DQ) for read and write operations. Both the DQ and DQS ports are bi-directional. Address ports are shared for write and read operations.

Although DDR2 SDRAM devices can use the optional differential strobes (DQS and DQS#), Stratix II, Stratix II GX, and Arria GX devices do not support this functionality. These devices only use the DQS signal to read from and write to the DDR2 SDRAM device. This is because DQS and DQS# pins are not differential I/O pins in these device families.

DDR2 SDRAM write and read operations support burst lengths of four and eight. This means that each read and write transaction transfers either four or eight groups of data. The latency between the time the read command is clocked into the memory and the time data is presented at the memory pins is called the column address strobe (CAS) latency. DDR2 SDRAM supports CAS latencies of two, three, four, and five. DDR2 SDRAM does not support half-clock latencies, unlike DDR SDRAM.

Altera® DDR2 SDRAM memory controllers only support burst length of four. In addition, these controllers do not support additive latencies offered by the DDR2 SDRAM devices.

DDR2 SDRAM devices use the SSTL-18 standard and can hold between 256 Mbytes to 4 Gbytes of data. Devices with capacities up to 512 Mbytes are divided into four banks and devices with capacities between one and four Gbytes are divided into eight banks. Only one row per bank can be accessed at one time. The ACTIVE command opens a row; the PRECHARGE command closes a row.

The Altera DDR2 SDRAM memory controller keeps a row open in every bank of your memory system. If you have a small DDR2 SDRAM device with 4 banks, the controller keeps track of four open rows, one per bank. If you have a dual-rank DDR2 SDRAM DIMM made up of devices with 8 banks each, then the controller tracks 16 open rows.

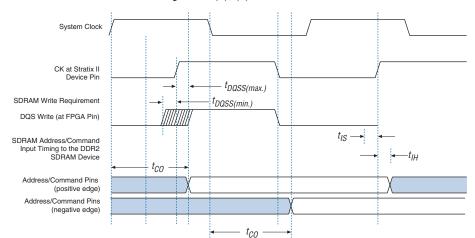

DDR2 SDRAM uses a delay-locked loop (DLL) inside the device to edge-align the DQ and DQS signals with respect to the CK and CK# signals. The DLL is turned on for normal operation and is turned off for debugging purposes. All timing analyses done in this document assume that the DLL inside the memory is on.

For more information about DDR2 SDRAM devices, refer to the www.jedec.org website.

DDR2 SDRAM devices have adjustable data-output drive strength, so Altera recommends that you use the highest drive strength of the memory for maximum performance. DDR2 SDRAM devices also offer on-die termination and output driver calibration. The on-die termination has an effective resistance of either 50  $\Omega$  75  $\Omega$  or 150  $\Omega$ . IBIS simulation can show the effects of different drive strengths, termination resistors, and capacitive loads on your system.

For a detailed discussion of the design trade-offs involved in selecting the best settings for your design, refer to *AN 408: DDR2 Memory Interface Termination, Drive Strength and Loading Design Guidelines.*

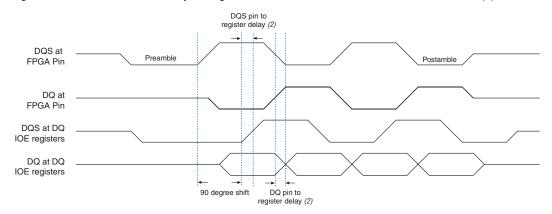

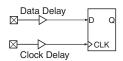

# Stratix II, Stratix II GX, and Arria GX Dedicated DQS Phase-Shift Circuitry

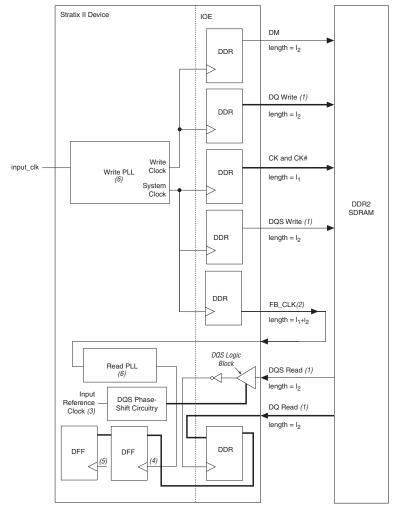

The dedicated phase-shift circuits are available at the top and the bottom sides of the Stratix II, Stratix II GX, and Arria GX devices. The circuit mainly consists of a DLL that generates the required phase shift setting for the incoming DQS read signal and DQS delay chains controlled by this DLL setting.

Using the dedicated phase shift circuitry allows you to capture data with the DQS sent by the memory device, which in turn results in higher performance than when not using the dedicated phase shift circuitry. When using the DQS signals to capture data in the FPGA, you can use the skew between the DQS and DQ signals to analyze read capture timing. When not using the DQS signals to capture data in the FPGA, you have to use the skew between the CK/CK# and DQ signals to analyze read capture margin. Skew reduces the read margin, and the skew between the CK/CK# and DQ signals is higher than the skew between the DQS and DQ signals. Therefore, the memory interface performance, when not using the DQS signal to capture data, is lower than the performance when using the DQS signal to capture data.

#### **ALTMEMPHY and Legacy PHY Brief Overview**

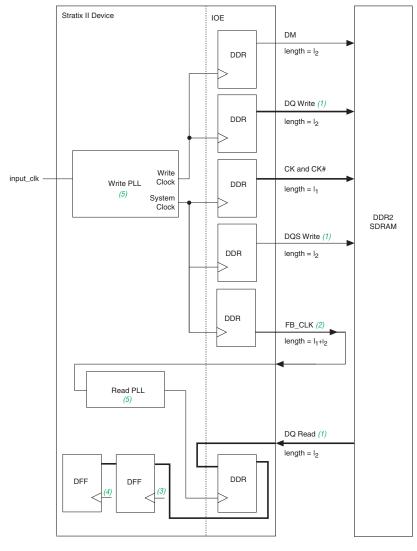

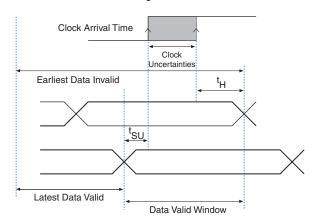

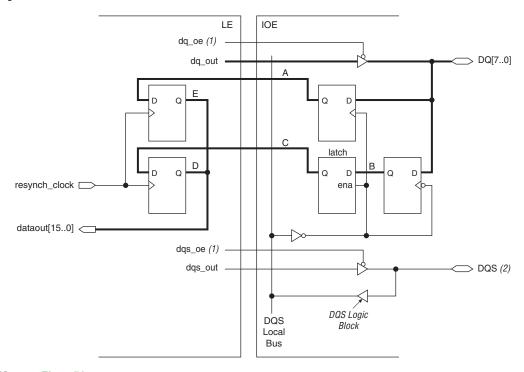

The legacy PHY uses a resynchronization clock with a static phase shift that is determined before design compilation, while the ALTMEMPHY implementation features a dynamic resynchronization clock that is calibrated for process (P) variations during initialization and tracks voltage and temperature (VT) variations.

The ALTMEMPHY megafunction is available as a stand-alone PHY for use with third-party memory controllers. The ALTMEMPHY is also instantiated by Altera's DDR and DDR2 SDRAM High Performance Controller MegaCore® function.

The legacy PHY is embedded in the DDR and DDR2 SDRAM Controller MegaCore function. Unlike ALTMEMPHY, the legacy PHY must be extracted manually from the DDR and DDR2 SDRAM Controller MegaCore function when using a third-party controller.

Use the ALTMEMPHY megafunction for all new designs to achieve high performance and optimal resynchronization phase shift. All new device families after Stratix II GX support ALTMEMPHY and may not support legacy PHY. Use legacy PHY when you need a lower latency interface or when you are not using dedicated phase shift circuitry.

#### **DDR2 SDRAM Interfaces in HardCopy II Devices**

Designs targeting the Stratix II device, up to 267 MHz, can be migrated to HardCopy® II devices. For the purpose of this application note, any Altera FPGA discussion referring to a Stratix II device can also apply to a HardCopy II device. HardCopy II device memory interfaces, however, have additional restrictions such as the usage of the PLL dedicated clock output pins for CK/CK# signals.

These restrictions are described in *AN 463: Using the ALTMEMPHY Megafunction with HardCopy II Structured ASICs* if you are using ALTMEMPHY, and in *AN 413: Using Legacy Integrated Static Data Path and Controller Megafunction with HardCopy II Structured ASICs* if you are using the legacy PHY.

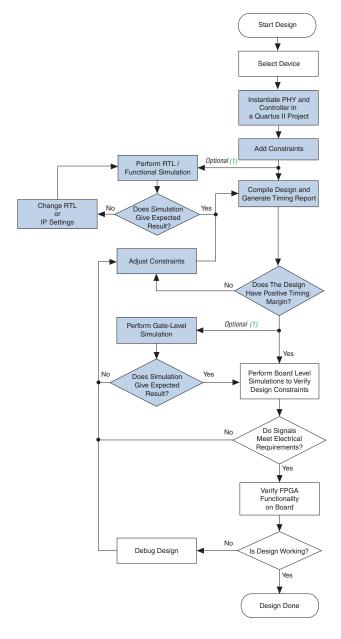

# Memory Interface Design Flow

This section outlines the Altera recommended flow, shown in Figure 1, for successful memory interface implementation in Stratix II, Stratix II GX, and Arria GX devices. These guidelines provide the best experience with external memory interfaces in these device families.

A detailed discussion of each step is available in *AN 449: Design Guidelines for Implementing External Memory Interfaces in Stratix II and Stratix II GX Devices*.

The next sections include two example designs that discuss the shaded design flow steps in Figure 1 in detail.

Refer to the *Quartus II Software Release Notes* for the Quartus II version that you are using for more information on possible issues with instantiation, simulation, and timing closure.

Figure 1. Design Flow for Implementing External Memory Interfaces in Stratix II, Stratix II GX, and Arria GX Devices

Note to Figure 1:

(1) Though optional, Altera recommends that you perform this step to ensure design functionality.

## **Design Checklist**

Table 3 contains a design checklist that you can use when implementing DDR2 SDRAM memory interfaces in Stratix II, Stratix II GX, and Arria GX devices.

Refer to AN 463: Using the ALTMEMPHY Megafunction with HardCopy II Structured ASICs if you are using ALTMEMPHY, or AN 413: Using Legacy Integrated Static Data Path and Controller Megafunction with HardCopy II Structured ASICs if you are using the legacy PHY, for any specific HardCopy II requirements.

Table 3. Checklist for Implementing DDR2 SDRAM Memory Interfaces in Stratix II, Stratix II GX, and Arria GX Devices (Part 1 of 4)

| Item          | Description                                                                                                                                                                                                                                                                                                                                                                                    | Yes or No |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

| Select Device |                                                                                                                                                                                                                                                                                                                                                                                                |           |  |

| 1             | Have you selected the memory interface frequency of operation and bus width? And, have you selected the FPGA device density and package combination that you will be targeting?  Ensure that the target FPGA device supports the desired clock rate and memory bus width. For detailed device resource information, refer to the device handbook chapter on external memory interface support. |           |  |

| 2             | Have you selected your PHY implementation? Use ALTMEMPHY whenever possible. Refer to TB 091: External Memory Interface Options for Stratix II Devices for more information on selecting between the two PHYs.                                                                                                                                                                                  |           |  |

|               | Instantiate PHY and Controller                                                                                                                                                                                                                                                                                                                                                                 |           |  |

| 3             | Have you parameterized and instantiated the PHY and controller for your target memory interface?                                                                                                                                                                                                                                                                                               |           |  |

|               | When instantiating multiple controllers, ensure effective sharing of device resources and appropriate constraints by referring to AN 462 Implementing Multiple Memory Interfaces Using the ALTMEMPHY Megafunction when using ALTMEMPHY and AN 392: Implementing Multiple Legacy DDR/DDR2 SDRAM Controller Interfaces when using legacy PHY.                                                    |           |  |

| 4             | If you are using your own controller, have you connected the PHY's local signals to your driver logic and the PHY's memory interface signals to top level pins?                                                                                                                                                                                                                                |           |  |

|               | Ensure that the local interface signals of the PHY are appropriately connected to your own logic. If the PHY is compiled without these local interface connections, you may encounter compilation problems when the number of signals exceeds the pins available on your target device.                                                                                                        |           |  |

|               | Functional Simulation                                                                                                                                                                                                                                                                                                                                                                          |           |  |

Table 3. Checklist for Implementing DDR2 SDRAM Memory Interfaces in Stratix II, Stratix II GX, and Arria GX Devices (Part 2 of 4)

| Item | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Yes or No |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5    | Have you simulated your design using the RTL functional model?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

|      | When using Altera's memory controllers, use the example design, which instantiates the PHY and controller blocks, along with the example driver/testbench module, and the memory device model. When using a custom memory controller, use the PHY functional simulation model in conjunction with your own driver logic/testbench and the memory device model.                                                                                                                                                                                                                                                                                                                                                           |           |

|      | Timing Closure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| 6    | Have you added constraints to the PHY and the rest of your design?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|      | The ALTMEMPHY megafunction is constrained when you use the generated synopsis design constraint (.sdc) file and .tcl files. However, you may need to adjust these settings to best fit your memory interface configuration.  The legacy PHY is constrained with an .sdc file generated by the DTW and .tcl file generated by the MegaWizard® Plug-In Manager.  Add pin assignment constraints and pin loading constraints to your design. Ensure that generic pin names used in the constraint scripts are modified to match your top-level pin names. Note that the loading on memory interface pins is dependent on your board topology (memory components, single DIMM, multiple DIMMs, single rank DIMM, and so on). |           |

|      | Add pin location constraints to all memory interface signals. Note that you need to place all the address and command pins on the same side of the device for optimal performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|      | Use board-level simulations to verify the default assignments created by the MegaWizard Plug-In Manager.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| 7    | Have you compiled your design and verified timing closure using all available models?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

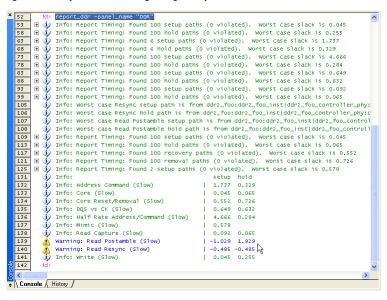

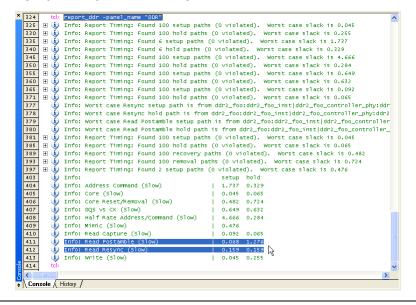

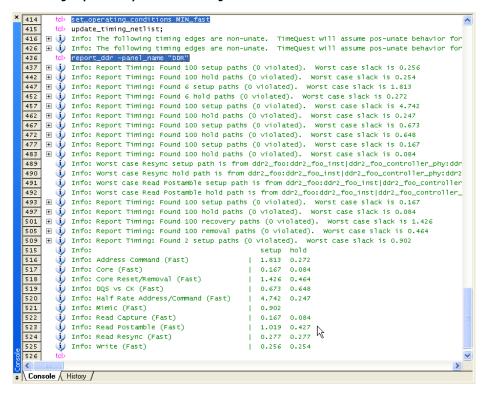

|      | Run the <b>Report DDR</b> TimeQuest task or source the < <i>variation_name</i> >_ <b>report_timing.tcl</b> file to generate a custom timing report for each of your ALTMEMPHY megafunction instances. Repeat this process using all device timing models (slow and fast).                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

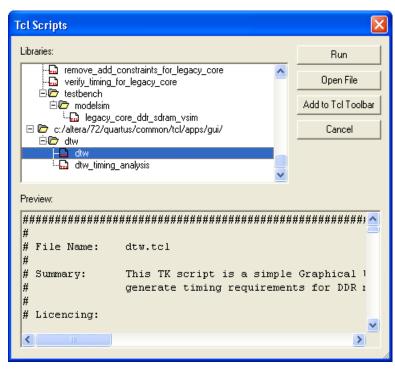

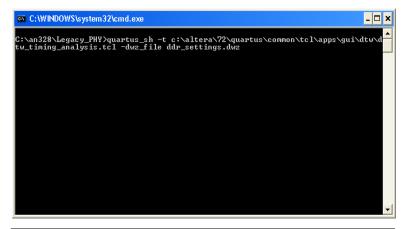

|      | Run the dtw_timing_analysis.tcl script for legacy PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| Table 3. Checklist for Implementing DDR2 SDRAM Memory Interfaces in Stratix II, Stratix II GX, and | d |

|----------------------------------------------------------------------------------------------------|---|

| Arria GX Devices (Part 3 of 4)                                                                     |   |

| AIIIA GA DEVICE | (Fail 3 VI 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Item            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes or No |  |  |

| 8               | If there are timing violations, have you adjusted your constraints to optimize timing?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |  |  |

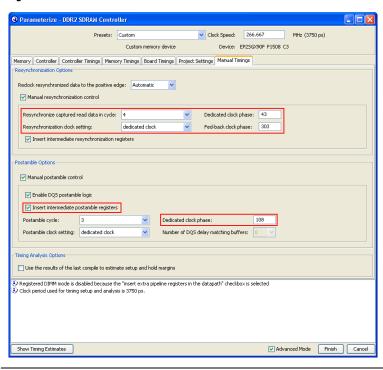

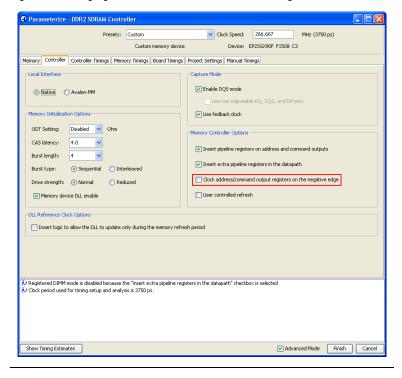

|                 | Adjust PLL clock phase shift settings or appropriate timing and location assignment to optimize margins for the various timing paths within the PHY. The ALTMEMPHY timing analysis script creates a panel that shows the timing margins in the Quartus II software compilation report. The dtw_timing_analysis.tcl script creates a clock phase shift recommendation panel in addition to the timing report panel in the Quartus II software compilation report.                                                                                                                                                                                                 |           |  |  |

|                 | Gate Level Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |  |  |

| 9               | Have you performed a timing simulation on your design?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |  |  |

|                 | Board Level Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |  |  |

| 10              | Have you selected the termination scheme and drive strength settings for all the memory interface signals on the memory side and the FPGA side?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |  |  |

|                 | Ensure that appropriate termination and drive strength settings are applied on all the memory interface signals, and verified using board level simulations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |  |  |

|                 | Stratix II, Stratix II GX, and Arria GX devices support on-chip termination. On the memory side, Altera recommends use of the DDR2 SDRAM on-die termination (ODT) feature whenever possible and use of external parallel termination on memory input signals that do not support the ODT feature.                                                                                                                                                                                                                                                                                                                                                                |           |  |  |

|                 | On the FPGA side, Altera recommends the <b>Series 25</b> $\Omega$ <b>without Calibration</b> OCT setting for bi-directional signals (such as DQ and DQS), and the <b>Series 50</b> $\Omega$ <b>without Calibration</b> OCT setting for unidirectional output signals to the memory (such as DM and address/command). If there are multiple loads on certain FPGA output pins (for example, when the address bus is driven to multiple memory devices on a DIMM), you may prefer to use the maximum drive strength setting over the series OCT setting. Note that when using the OCT feature on the FPGA, the programmable drive strength feature is unavailable. |           |  |  |

|                 | Use board-level simulations to pick the optimal setting for best signal integrity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |  |  |

| Item | Description                                                                                                                                                                                                  | Yes or N |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 11   | Have you performed board-level simulations to ensure electrical and timing margins for your memory interface?                                                                                                |          |

|      | Ensure you have a sufficient eye opening using simulations. Be sure to use the latest FPGA and memory IBIS models, board trace characteristics, drive strength, and termination settings in your simulation. |          |

|      | You must use any timing uncertainties at the board level that you calculate using such simulations to adjust the input timing constraints to ensure the accuracy of Quartus II timing margin reports.        |          |

|      | System Verification                                                                                                                                                                                          |          |

| 12   | Have you verified the functionality of your memory interface in system? You can use the SignalTap® Logic Analyzer to verify the interface signal behavior.                                                   |          |

Example

Walkthrough for

333-MHz DDR2

SDRAM

Interface Using

ALTMFMPHY

This walkthrough describes the steps necessary to create, constrain, and verify operation of a 72-bit wide, 333-MHz/667-Mbps DDR2 SDRAM memory interface targeted for the Stratix II GX PCI Express Development Board. This example design (an already completed version is available for download with this application note) uses the ALTMEMPHY megafunction-based DDR2 SDRAM High Performance Controller MegaCore to interface memory on the Stratix II GX PCI Express Development Board.

If you are using the legacy PHY, go to the "Example Walkthrough for 267-MHz DDR2 SDRAM Interface Using the Legacy PHY" on page 54.

The ALTMEMPHY megafunction is a memory interface PHY that enables speeds of up to 333 MHz on Stratix II and Stratix II GX devices, 267 MHz on HardCopy II devices, and 233 MHz on Arria GX devices. This PHY uses dedicated DQS phase-shift circuitry for capturing data from memory and a dynamic clock calibration scheme to resynchronize memory read data to the system clock domain. This auto-calibrated solution tracks the changes in voltage and temperature (VT), and simplifies timing closure and clock phase shift selection. The ALTMEMPHY megafunction is used to implement the datapath in the DDR2 SDRAM High Performance Controller MegaCore.

For more information about the PHY and memory controller, refer to the *ALTMEMPHY Megafunction User Guide* and the *DDR and DDR2 SDRAM High Performance Controller User Guide*, respectively.

The Stratix II GX edition of the Altera's PCI Express Development Kit delivers a complete PCI Express-based development platform. This PCI Express solution, interoperable with industry-standard PCI Express platforms, facilitates the development of custom PCI Express applications.

For more information about PCI Express development, refer to the *Stratix II GX PCI Express Development Kit* web page.

This example design walks through the memory interface design flow steps, shown in Figure 1 on page 7

For more information about the memory interface design flow refer to AN 449: Design Guidelines for Implementing External Memory Interfaces in Stratix II and Stratix II GX Devices.

The example design was created using Quartus II software version 7.2 and MegaCore IP Library software version 7.2.

While this example focuses on the Stratix II GX device family, the information is also applicable to the ALTMEMPHY-based memory interface designs targeting Stratix II, Arria GX, and HardCopy II devices. However, pay attention to the restrictions for HardCopy II devices described in *AN 463: Using ALTMEMPHY Megafunction with HardCopy II Structured ASICs.*

#### Step 1: Select Device

This example design uses the EP2SGX90FF1508C3 device that comes with the Stratix II GX PCI Express Development Board. The board is also equipped with five 333-MHz-capable DDR2 SDRAM devices: four  $\times 16$  devices with part number: MT47H32M16CC-3 and one  $\times 8$  device with part number MT47H64M8CB-3.

For more information about all the features of the board, refer to the *Stratix II GX PCI Express Development Board Reference Manual*.

The example design uses the five DDR2 memory devices to create a 72-bit interface running at 333 MHz using the ALTMEMPHY-based DDR2 SDRAM High Performance Controller MegaCore function. This is considered a width-expansion interface since multiple memory devices are used to create one wide interface controlled by a single memory controller.

The maximum number of interfaces you can implement on any given device is limited by resource availability (number of DQ groups of desired width, user I/O pins, PLLs, DLLs, clocks, and FPGA core resources). For example, the Stratix II GX EP2SGX90FF1508C3 device supports nine ×8 DQ groups each on the top and bottom sides of the device. The DLL located on the top (or bottom) can be shared amongst all nine DQ groups on that side of the device as long as they are implementing memory interfaces running at the same frequency. The example 72-bit interface uses all nine of the groups available on the bottom side (I/O banks 7 and 8). The remaining nine DQ groups located on the top side of the device can be used for other memory interfaces. The PHY also uses one enhanced PLL to generate the 6 clock signals required for each memory interface. The remaining three enhanced PLLs are available for use by other memory interfaces and user logic.

Refer to the *External Memory Interfaces* chapter of the appropriate device handbook (Stratix II, Stratix II GX, or Arria GX) to determine the number DQ groups of each width supported by the FPGA.

Expanding your memory interfaces for width or depth with the same memory controller (shared address and command bus) is supported natively by the MegaWizard Plug-In Manager. Creating multiple memory controllers with independent memory transactions (independent address and command buses) requires you to create a unique megafunction variation for each interface. Sharing device resources between multiple memory interfaces may require RTL modifications.

Both the MT47H32M16CC-3 and the MT47H64M8CB-3 devices have the same timing specifications and share the same data sheet. If you are using devices with different timing specifications, choose the worst specifications.

### Step 2: Instantiate PHY and Controller in a Quartus II Project

Begin your memory interface design by instantiating the PHY and controller modules. Figure 2 shows a system-level diagram including the top-level example design that the DDR2 SDRAM High Performance Controller MegaCore function creates for you.

The example design is a fully functional design that can be simulated, synthesized, and used in hardware. It contains the PHY, controller, and an example driver. The example driver is a self-test module that issues read and write commands to the controller and checks the read data to produce the pass/fail and test-complete signals.

Pass or Fail

Example Driver

Local Interface

Local Interface

DDR SDRAM

High Petromance

Controller

Figure 2. System-Level Diagram of DDR2 SDRAM Interface

Note to Figure 2:

(1) The PLL and DLL modules are included in the ALTMEMPHY megafunction.

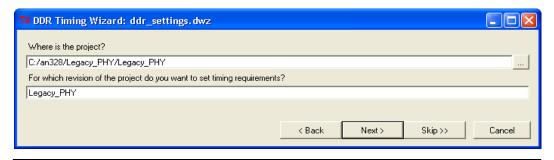

To instantiate the PHY and controller, follow these steps:

- 1. There are two options for step 1:

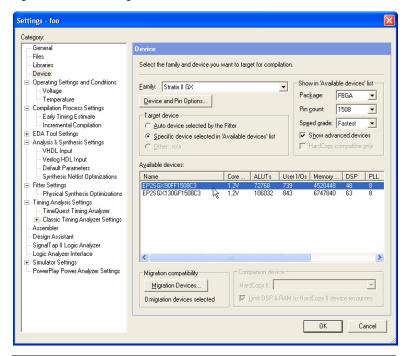

- a. Create a new Quartus II project or open an existing project where you would like to implement the DDR2 SDRAM memory interface. When creating a new project, specify the target FPGA device on page 3 of the New Project Wizard: Family and Device Settings. Set Stratix II GX as the Family and choose the EP2SGX90FF1508C3 device from the Available devices list.

or

b. When using an existing project, set the target FPGA device by going to the Assignments menu and selecting **Device...**. In the window appears, set **Stratix II GX** as the **Family**, and choose the **EP2SGX90FF1508C3** device from the **Available devices** list, as shown in Figure 3. Device listings displayed are filtered by the fastest speed grade and 1508-pin FPGA package. The Quartus II project name for this example design is **foo**.

Refer to the Tutorial in the *Quartus II Online Help* for step-by-step instructions for creating a Quartus II software project.

Figure 3. Select the Target FPGA Device in Quartus II Software

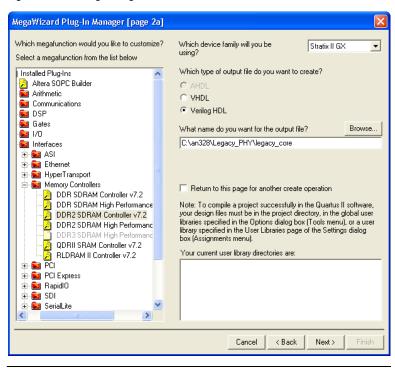

2. In the Quartus II software, on the Tools menu point to MegaWizard Plug-In Manager. Select Create a new custom megafunction variation and click Next (see Figure 4). You now are looking at MegaWizard Plug-In Manager [page 2a] (Figure 5).

Figure 4. Launch the MegaWizard Plug-In Manager

Under Select a megafunction from the list below, click the "+" icon to expand Interfaces. Click the "+" icon to expand Memory

Controllers and select the DDR2 SDRAM High Performance

Controller v7.2 megafunction, as shown in Figure 5.

If Memory Controllers is not listed under the Interfaces directory, ensure that you installed the IP Library and specified the installation directory location as a User Library if the default location (c:\altera\<version>\ip) was not used.

If the controller megafunction is listed but grayed out, ensure that the correct device family is selected in the drop-down menu located in the top right-hand corner of the window MegaWizard Plug-In Manager [page 2a].

MegaWizard Plug-In Manager [page 2a] Which megafunction would you like to customize? Which device family will you be Stratix II GX using? Select a megafunction from the list below 🖃 💽 Installed Plug-Ins Which type of output file do you want to create? Altera SOPC Builder

Arithmetic O VHDL E SOMMunications

DSP Verilog HDL ⊕ 🙀 Gates What name do you want for the output file? Browse.. 🕁 🔯 I/O C:\Designs\SII\_GX\_DDR2\_333MHz\_PCle\ddr2\_foo interfaces ASI

Ethernet Return to this page for another create operation DDR SDRAM Controller DDR SDRAM High Perfo Note: To compile a project successfully in the Quartus II software, DDR2 SDRAM Controller your design files must be in the project directory, in the global user DDR2 SDRAM High Performance Controller v7.2 d in the Options dialog box (Tools menu), or a user box (Assignments menu). QDRII SRAM Controller v Your current user library directories are: RLDRAM II Controller v7. ⊕ 🔯 PCI 🗓 🔯 PCI Express 🛨 🔯 RapidlO ⊕ 🔯 SDI 🛨 🔯 SerialLite < Back Next> Cancel

Figure 5. Select the MegaCore Function

4. Select the type of output files you want the MegaWizard to create. For this example design, select **Verilog HDL**.

5. Specify the output file name for this megafunction variation. The MegaWizard Plug-In Manager shows the project path that you specified when creating the project. Append a variation name for the MegaCore function output files project path>\<variation name>.

Enter **ddr2\_foo** as the variation name for this example design.

The variation name must be different from the project name, which is **foo**.

Figure 5 shows the MegaWizard after these settings have been specified.

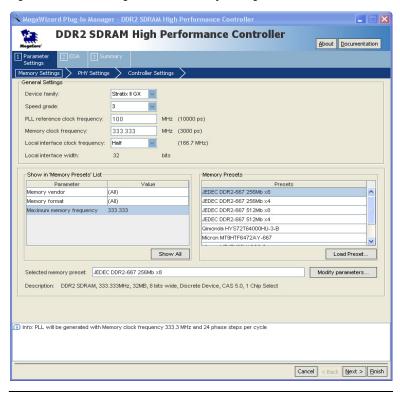

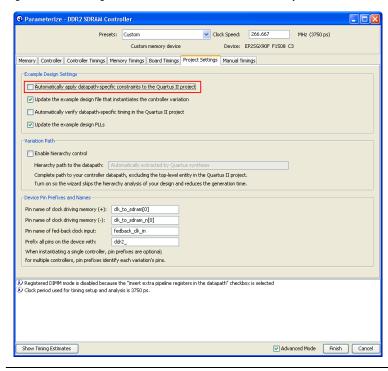

- 6. Click **Next**. This launches the **Memory Settings** panel, located under the **Parameter Settings** tab in the MegaWizard (Figure 6). In the **Memory Settings** panel, you can parameterize the DDR2 SDRAM High Performance Controller MegaCore function.

- In the Parameter Settings tab of the MegaWizard Plug-In Manager, there are three categories of parameters that you can set: Memory Settings, PHY Settings, and Controller Settings. Start with the Memory Settings tab, as shown in Figure 6.

Figure 6. Controller MegaWizard – Memory Settings

- 8. Verify that the target **Device family** is set to **Stratix II GX**.

- 9. Select the **Speed Grade** option for the target device. Since the PCI Express Development Board includes a -3 speed grade FPGA device, select **3** from the drop-down list. The -3 speed grade supports the 333-MHz DDR2 SDRAM memory interface clock rate you intend to implement (based on the specifications listed in Table 1 and the *Stratix II GX Device Handbook*).

- Specify the PLL reference clock frequency option as 100 MHz. The PCI Express Development Board includes a 100-MHz oscillator that feeds the clock input pins on the bottom I/O banks of the Stratix II GX device.

11. Specify the **Memory clock frequency** option as **333.333** MHz. Be sure to specify three decimal digits for non-integer frequencies to ensure that proper timing constraints and PLL settings are generated. Verify that the period reported in parentheses by the MegaWizard is accurate.

After you specify the PLL reference and memory clock frequencies, the MegaWizard determines if valid PLL settings exists to perform the necessary frequency synthesis. When successful, an Info message is generated in the bottom pane of the MegaWizard (see Figure 6).

For example, in the example design presented in this application note, the MegaWizard reports "Info: PLL will be generated with Memory clock frequency 333.3 MHz and 24 phase steps per cycle." The "24 phase steps per cycle" refers to the resolution of the PLL phase shift stepping feature available for the calibration block to place the resynchronization clock within the data valid window.

- 12. Select the Local interface clock frequency option. You can choose between Half and Full, which refers to the relationship between the clock rate at the local side compared to the memory side. In half-rate mode, the local side operates at half the memory clock frequency. Since the full-rate mode does not support the example design's target memory clock rate of 333.333 MHz, select Half. The resulting local interface frequency is 166.667 MHz.

- 13. To specify the external memory device specifications, select a Memory Preset from the list of presets that matches your memory. You can use the filters provided in a list to the left of the panel to sort through the list of memory presets.

Select **333.333** from the **Maximum memory frequency** filter. Only memory presets that meet that clock rate are now displayed. Since a preset for the MT47H32M16CC-3 or MT47H64M8CB-3 device is not available, select a preset that is most similar. Use this as a base preset and modify as necessary.

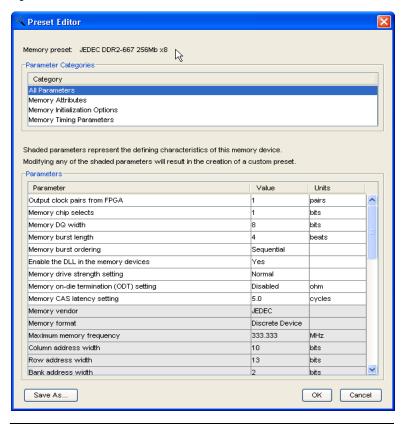

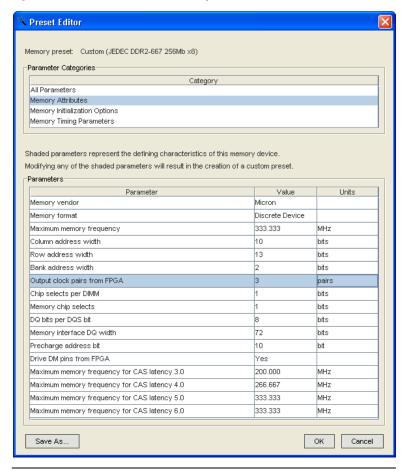

14. Select the JEDEC DDR2-667 256-Mb ×8 preset. Select Modify parameters..., this launches the Preset Editor, as shown in Figure 7.

The **All Parameters** category is selected by default, and the current list of settings are displayed in the **Parameters** section of the panel. The cells with white backgrounds are programmable features supported by the memory. The cells with gray background are defining characteristics of the memory device. Changing any of these settings creates a custom variation of the preset that you can use in current and future designs.

Figure 7. Preset Editor - JEDEC DDR2-667 256Mb ×8

- 15. Modify the parameters listed in the **Preset Editor** dialog box to match the specifications from the Micron MT47H32M16CC-3 and MT47H64M8CB-3 datasheet.

- a. Select the **Memory Attributes** category and make the modifications shown in Figure 8.

- b. Change Memory vendor from JEDEC to Micron.

- c. Change Output clock pairs from FPGA from 1 to 3. The PCI Express Development Board shares one pair of CK/CK# clock outputs for every two ×16 DDR2 devices and drives one pair of CK/CK# clock outputs to the ×8 DDR2 device, so the 72-bit interface needs three pairs of CK/CK# outputs.

- d. Change **Memory DQ width** from **8** to **72** since you are implementing a **72**-bit DDR2 interface.

- e. Change Maximum memory frequency for CAS latency 3.0 to 200.000 MHz based on the specifications from the Micron datasheet.

- f. Similarly, change **Maximum memory frequency for CAS** latency **4.0** to **266.667** MHz.

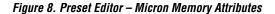

g. Select the Memory Initialization Options category shown in Figure 9. Verify that the Memory on-die termination (ODT) setting is set to Disabled since the Stratix II GX PCI Express Board features external termination on all memory interface signals.

Rreset Editor Memory preset: Custom (JEDEC DDR2-667 256Mb x8) Parameter Categories Category All Parameters Memory Attributes Memory Initialization Options Memory Timing Parameters Shaded parameters represent the defining characteristics of this memory device. Modifying any of the shaded parameters will result in the creation of a custom preset. Parameters Parameter Value Units Memory burst length beats Memory burst ordering Sequential Enable the DLL in the memory devices Yes Memory drive strength setting Normal Memory on-die termination (ODT) setting Disabled ohm Memory CAS latency setting 5.0 cycles Save As. OK Cancel

Figure 9. Preset Editor – Micron Memory Initialization Options

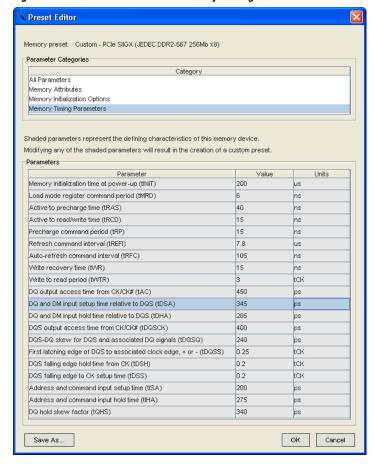

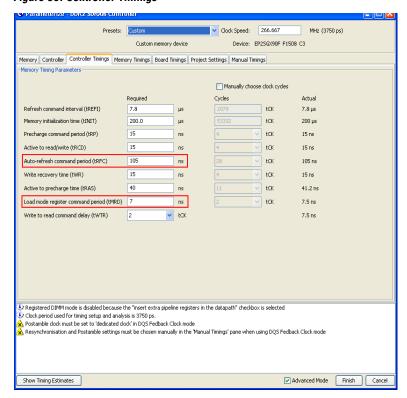

h. Select the **Memory Timing Parameters** category and make the modifications based on the Micron datasheet shown in Figure 10.

Figure 10. Preset Editor – Micron Memory Timing Parameters

- i. Change tRAS from 45 to 40 ns.

- j. Change tREFI from 7 to 7.8 us.

- Change tRFC from 75 to 105 ns.

I. De-rate the data setup and hold requirements based on FPGA output edge rates and DQS strobe type. The Stratix II GX device only supports single-ended DQS strobes and has typical edge rates of approximately 1 V/ns. The de-rated timing requirements for this edge rate and strobe type are 345 ps setup time and 285 ps hold time, as specified in the Micron datasheet. You need to verify these typical edge rates for each system using board-level simulations.

- m. Change tDSA from 100 ps to 345 ps. Change tDHA from 175 ps to 285 ps.

- n. Similarly, de-rate the address and command setup and hold requirements based on the FPGA output edge rate.

- Click Save As... and save this custom memory preset as Custom – PCIe SIIGX (JEDEC DDR2-667 256Mb ×8).

The presets are stored in the MegaCore **\lib** directory by default (for example,

<quartus\_installation\_directory>\ip\ddr2\_high\_perf\lib) and are

available for use in future projects. If you save your custom

memory preset in a different directory, you can use the Load

Preset... feature in the Memory Settings panel to target that

memory device (Figure 6 on page 18).

- p. Click **OK** to return to the **Memory Settings** panel.

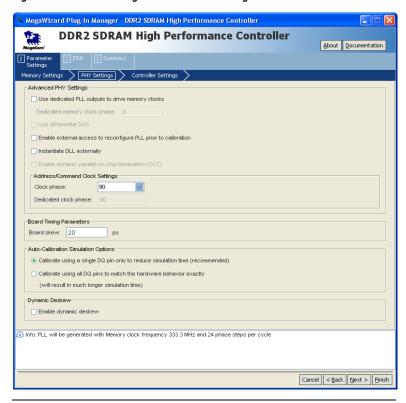

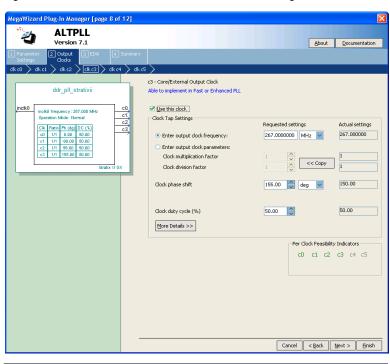

- 16. You have now specified all the memory settings. Click **Next** to specify the PHY settings (Figure 11).

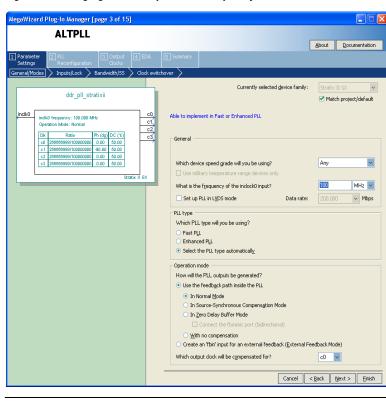

Figure 11. Controller MegaWizard - PHY Settings

- 17. In the **Advanced PHY Settings** section of the **PHY Settings** panel, you can enable certain advanced features of the PHY.

- a. For designs targeting HardCopy II devices, enable the Use dedicated PLL outputs to drive memory clocks feature and the Enable external access to reconfigure PLL prior to calibration feature. These options are not enabled for the Stratix II GX example design presented in this application note.

- For designs sharing DLLs across multiple memory interfaces, enable the Instantiate DLL externally option. This option is not enabled for the single memory interface example design.

- c. Observe the **Clock phase** setting used to generate the address and command signals output to the memory. The choices available for Stratix II, Stratix II GX, and Arria GX devices are **0**, **90**, **180**, and **270** degrees of offset from the full-rate clock (mem\_clk\_2x) used to generate the CK/CK# signals. These clock phases are generated using the rising and falling edges of the mem\_clk\_2x and write\_clk\_2x clocks of the ALTMEMPHY megafunction. You can alter the default clock phase of **90** degrees selection to optimize timing margins for the address/command timing path.

- 18. Specify the Board skew (in picoseconds) across all memory interface signals in your design, in the Board Timing Parameters region of the PHY Settings panel. The specified skew is across all memory interface signal types including data, strobe, clock, address and command, and is used to generate the PHY timing constraints for all paths.

- 19. Choose the Auto-Calibration Simulation Options for your design. The recommended setting is Calibrate using a single DQ pin only to reduce simulation time. This setting only affects functional simulation.

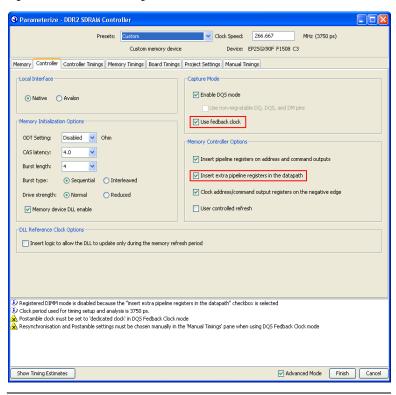

- 20. You have now specified all the PHY settings. Click **Next** to specify the controller settings (Figure 12).

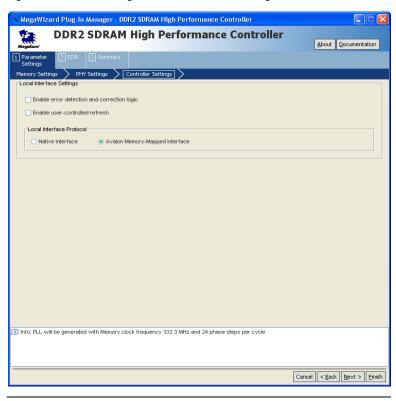

Figure 12. Controller MegaWizard – Controller Settings

21. Specify your preference in the Local Interface Settings in the Controller Settings panel.

The example design uses the defaults options and therefore no changes are required on this panel.

- Select the Enable error detection and correction logic option to enable ECC.

- b. Check the Enable user-controller refresh feature if you wish to optimize latency by controlling when the controller issues refreshes to the memory.

- c. Select the **Local Interface Protocol** for the memory interface. The default interface is the **Avalon Memory-Mapped Interface** that allows you to easily connect to other Avalon® Memory-Mapped peripherals.

For more information about the Avalon Memory-Mapped interface, refer to the Avalon Memory-Mapped Interface Specification.

- 22. You have now specified the controller settings. Click Next.

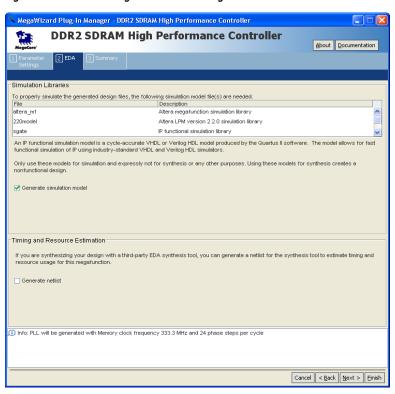

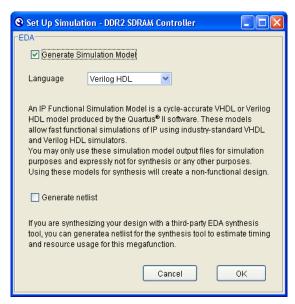

- 23. In the **EDA** tab of the MegaWizard shown in Figure 13, enable the **Generate Simulation Model** option. Choose between the **Verilog HDL** or **VHDL** language options and click **Next**.

Figure 13. Controller MegaWizard – EDA Page

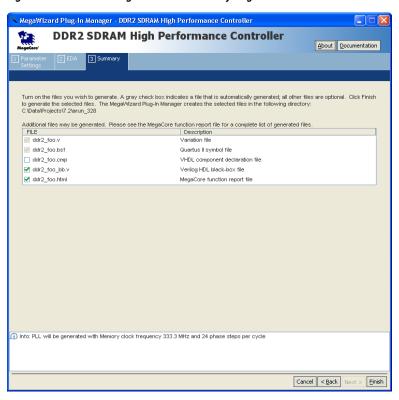

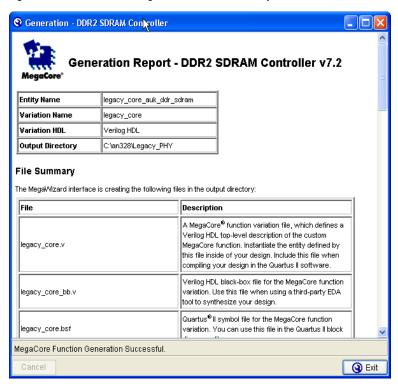

24. You have now fully parameterized the PHY and memory controller. The **Summary** tab, shown in Figure 14, allows you to select optional files that the MegaWizard can generate for you. Click **Finish** to generate the megafunction variation.

Figure 14. Controller MegaWizard – Summary Page

25. The MegaWizard generates all the files necessary to constrain, compile, simulate, and timing analyze your memory interface design. Figure 15 shows the messages printed by the MegaWizard while generating your megafunction variation. This dialog box also provides recommendations about applying constraints on your design. These messages are described in the section "Step 3: Add Constraints" on page 31.

Generation - DDR2 SDRAM High Performance Controller 7.2 Info: Generating the Example Design. info: Generating the Pin Planner file. Info: Generating the Functional Simulation Model info: Generating the Synopsys Design Constraints file. info: Generating the Timing Report script. Info: Generating the ALTPLL Megafunction instance. info: Generating the ALTMEMPHY Megafunction instance. info: Generating the ALTPLL\_RECONFIG Megafunction instance. 🔟 Info: Generating the Functional Simulation Model 🔟 Info: Before compiling your variation in Quartus II, you should follow these steps: Info: - Enable TimeQuest under Settings, Timing Analysis Settings. Info: - Add the ddr2\_foo\_phy\_ddr\_timing.sdc file to your Quartus II project. Info: - Add I/O Standard assignments by running the ddr2\_foo\_pin\_assignments.tcl script. Info: - Set the Default I/O standard to match the memory interface I/O standard setting. 🔟 Info: - Turn on Optimize hold timing and select All paths in the Quartus II Fitter Settings. Info: - Please make sure that address/command pins are placed on the same edge as the CK/CK# pins. Info: - Set the top level entity of the project to ddr2\_foo\_example\_top. i Info: See the User Guide for more detail: Generation Successful Exit Cancel

Figure 15. MegaWizard Messages and Constraint Recommendations

You have now successfully instantiated the PHY and controller in your design.

Table 4 is a partial list of the files generated by the DDR2 SDRAM High Performance Controller MegaWizard and content descriptions.

| Table 4. Files Generated by the Controller MegaWizard (Part 1 of 2) |                                                                                                                                                                                     |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Name                                                           | Description                                                                                                                                                                         |  |

| <variation_name>.v(hd)</variation_name>                             | MegaCore variation file.                                                                                                                                                            |  |

| <variation_name>_example_top.v(hd)</variation_name>                 | Example top-level design file that can be simulated, synthesized, and used in hardware. Instantiates the PHY, controller, and a driver.                                             |  |

| <variation_name>_example_driver.v(hd)</variation_name>              | Example driver (self-test module) that issues reads and writes to the controller to check functionality.                                                                            |  |

| <variation_name>_ddr_timing.sdc</variation_name>                    | Sets timing constraints for the ALTMEMPHY megafunction instance.                                                                                                                    |  |

| <variation_name>_pin_assignments.tcl</variation_name>               | Adds I/O standard settings for all memory interface pins, and adds output enable group assignments to ensure VREF rules are met when the design contains input/bi-directional pins. |  |

| <variation_name>_phy_report_timing.tcl</variation_name>             | Generates a detailed timing report for all timing paths in the ALTMEMPHY instance.                                                                                                  |  |

| Table 4. Files Generated by the Controller MegaWizard (Part 2 of 2)                        |                                                                                                        |  |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| File Name                                                                                  | Description                                                                                            |  |  |

| <pre><variation_name>_auk_ddr_hp_controller_wrapper. vo or .vho</variation_name></pre>     | Verilog HDL or VHDL functional simulation model of the memory controller.                              |  |  |

| <pre><variation_name>_phy_alt_mem_phy_sequencer_ wrapper.vo or .vho</variation_name></pre> | Verilog HDL or VHDL functional simulation model of the memory interface PHY.                           |  |  |

| testbench\ <variation_name> _example_top_tb.v or .vhd</variation_name>                     | Verilog HDL or VHDL testbench for functional simulation with memory controller, PHY, and memory model. |  |  |

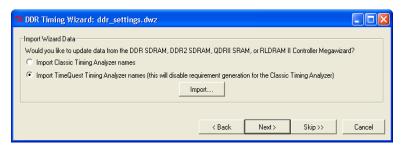

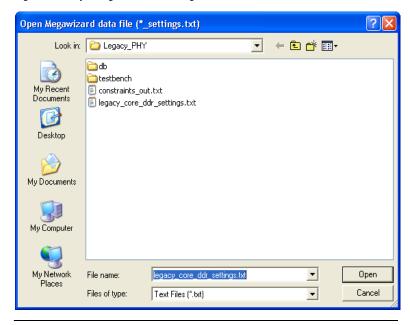

#### **Step 3: Add Constraints**

All memory interface designs require timing constraints and I/O assignments (including I/O standard, output pin loading, termination, drive strength, and pin location assignments). Most of these constraints are generated for you by the MegaWizard Plug-In Manager. The MegaWizard Generation dialog box (Figure 15 on page 30), provides instructions on how to apply these constraints to your design.

To apply all necessary constraints to your design, follow these steps:

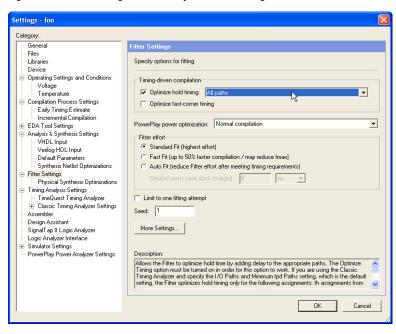

- 1. In the Quartus II software, on the Assignments menu, click **Settings.**

- 2. On the left side of the **Settings** dialog box, under the **Category** list, click **Fitter Settings**. The **Fitter Settings** panel appears.

- 3. In the **Fitter Settings** panel, turn on the **Optimize hold timing** option. On the drop-down menu next to the option you have just enabled, select **All paths**, as shown in Figure 16.

For ALTMEMPHY designs targeting memory clock frequencies of 267 MHz and above, select the **Standard Fit** option under the **Fitter effort** section of the **Fitter Settings** panel. This option optimizes placement of the resynchronization and postamble registers in such designs.

4. Click OK.

Figure 16. Fitter Settings for Memory Interface Designs

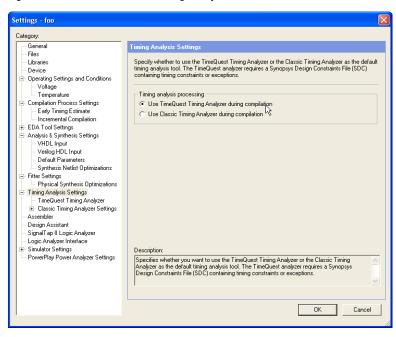

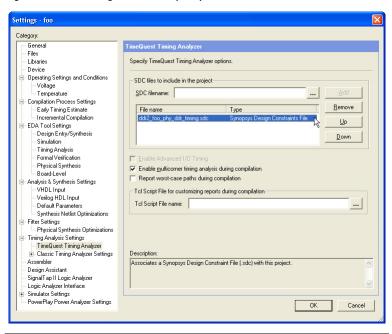

- 5. Enable the TimeQuest Timing Analyzer. On the Assignments menu, click **Settings**. The **Settings** dialog box appears.

- 6. In the **Settings** dialog box, under the **Category** list, click **Timing Analysis Settings**. In the panel that appears to the right, select **Use TimeQuest Timing Analyzer during compilation**, as shown in Figure 17.

Figure 17. Enable TimeQuest Timing Analyzer

- Under the list Category, click the "+" icon next to Timing Analysis Settings and select Time Quest Timing Analyzer.

- Add the Synopsys design constraints .sdc file, <variation\_name>\_phy\_ddr\_timing.sdc, to your project. This file contains all the timing constraints for the PHY. Browse to the .sdc file, select it and click Add. The file name appears in the .sdc file list.

- 9. Click **OK** (see Figure 18).

The **.sdc** timing constraints file is not added to the Quartus II software project automatically, and must be manually included in the project during compilation for successful timing closure and operation.

Figure 18. Add Timing Constraints (SDC)

- 10. Set the top-level entity to the example project:

- a. On the File menu, click **Open**.

- b. Browse to <*variation\_name*>\_example\_top.v(hd) file and click Open.

- c. On the Project menu, click Set as Top-Level Entity.

If you are not using the example design, but instead are implementing the DDR2 SDRAM interface in your own top-level Quartus II software project, instantiate the *<variation\_name>.v(hd)* module in your design and continue with the design flow.

- 11. On the Processing menu, point to Start and click Start Analysis & Synthesis. This step ensures your designs files are in order and creates a list of nodes that can be accessed to create design constraints.

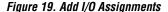

- 12. Add the I/O assignments.

a. The I/O standard and output enable group assignments are specified in the <variation\_name>\_pin\_assignments.tcl file.

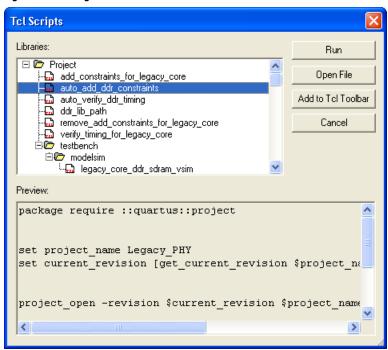

If your design uses the default top-level pin names for memory interface signals as in this walkthrough (names that start with the "mem\_" prefix, such as mem\_dq and mem\_dqs), select Tcl Scripts... from the Tools menu.

- b. In the **Tcl Scripts** dialog box, select <*variation\_name*>**pin\_assignments.tcl**.

- c. Click **Run**, as shown in Figure 19.

If you are not using the default pin names and wish to add a unique prefix to memory interface pin names (this is recommended when implementing multiple controllers on the same device), use the **Pin Planner** file generated by the MegaWizard to import pin assignments.

- In the Quartus II software, on the Assignments menu, click Pin Planner. In the Pin Planner, edit your top-level design to add a prefix to all DDR2 SDAM interface signal names.

For example, change mem\_addr to core1\_mem\_addr.

- On the Assignments menu, click Pins. Right-click in the window and click Create/Import Megafunction. Select

- **Import an existing custom megafunction** and navigate to <*variation\_name>*.ppf.

- Type the prefix that you added to your top-level DDR2 SDRAM interface signal names into the Instance name dialog box and click OK.

- d. Add the I/O pin location assignments.

Use the **Pin Planner** feature or the **Assignment Editor** to create pin location assignments for all memory interface signals. You can choose which DQS pin groups should be used by assigning each DQS pin to the required pin. The Quartus II Fitter then automatically places the respective DQ signals onto suitable DQ pins within each group. Alternatively, you can manually specify all DQ and DQS pins to align your project with your PCB requirements.

- Create pin assignments for the PLL reference clock pin, clock\_source, and the reset pin, global\_nreset. Also, when using this example design, create pin assignments for the test complete and pnf (pass not fail) signals.

- "Appendix A: Stratix II GX PCI-Express Development Board Pin Assignments" on page 105 contains the list of memory interface pin names and locations for the Stratix II GX PCI Express Development Board.

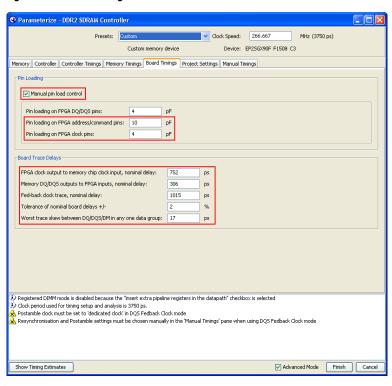

- e. Add the output pin load assignments. The loading for the various output and bi-directional pins on the Stratix II GX board are as follows:

- Two of the CK and CK# clock pairs have two loads = 2 × 2 pF = 4 pF. The third CK/CK# clock output pair that drives the ×8 DDR2 devices has one load = 2 pF.

- DQ and DQS pins (one load) = 4 pF

- Addr/Cmd pins (five loads) =  $5 \times 2 pF = 10 pF$

- f. Add **Termination** or **Current Strength** assignments. The default Altera recommendations for termination settings are:

- Series 25 Ohms without Calibration for the bi-directional DQ and DQS signals.

- Series 50 Ohms without Calibration for all output pins including DM, address, command, and clock signals.

Altera recommends using the memory's on-die termination (ODT) feature when it is suitable for your system; however, the Stratix II GX PCI board features external termination on the memory side for all memory interface signals. Therefore, this example does not use memory ODT  $\Omega$  or the FPGA on-chip termination features. Instead, the example design uses the SSTL-18 Class I I/O standard along with the Maximum Current strength for all signals (including DQ and DQS).

After executing the *<variation\_name>\_pin\_assignments.tcl* file, use the **Assignment Editor** to make the following changes:

- Replace the SSTL-18 Class II I/O standard setting on all DQ and DQS pins (named mem\_dq and mem\_dqs) with the SSTL-18 Class I setting.

- Delete the Termination setting of Series 50- or 25-Ohms without Calibration on all the DQ, DQS, DM, and CK/CK# pins (named mem\_dq, mem\_dqs, mem\_dm, mem\_clk, and mem\_clk n).

- Add a Current Strength assignment set to Maximum Current for all DQ, DQS, DM, and CK/CK# pins.

- You should perform board simulations to validate if these recommendations are optimal for your system. Refer to "Step 8: Perform Board-Level Simulations to Verify Design Constraints" on page 103 for more information.

- The drive strength feature is unavailable on the FPGA device when the OCT feature is enabled. If board simulations indicate that the OCT setting is not appropriate for your system, use simulations to determine the optimal drive strength setting and add that constraint to your Quartus II project.

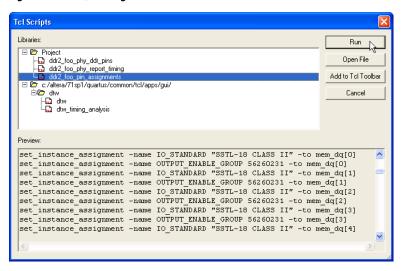

The pin location and output pin load assignments for the Stratix II GX PCI Express Board can be imported:

- 1. In the Quartus II software, on the Assignments menu, click **Import**Assignments....

- When the Import Assignments dialog box appears, click the ...

button to browse for the file (located in the downloadable example

design archive shown in Figure 20)

AN328\_ALTMEMPHY\_Assignments.CSV and select it.

This file also includes pin assignments for the clock source, test complete, and pass/fail signals used by the top-level example design file, as well as assignments to reserve unused DDR2 memory pins (A13, A14, and BA2) as **Outputs Driving Ground**.

The termination and other I/O settings used in the example design are also listed in "Appendix A: Stratix II GX PCI-Express Development Board Pin Assignments" on page 105.

Figure 20. Import CSV Assignments

You have now applied all the required design constraints for this memory interface design.

# Step 4: Perform RTL/Functional Simulation (Optional)

You can simulate the memory interface with the MegaWizard Plug-In Manager-generated IP functional simulation model. You should use this model in conjunction with your own driver or the testbench generated by the MegaWizard that issues read and write operations and a memory model.

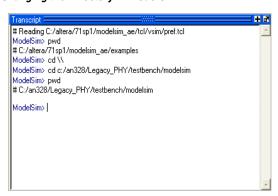

Use the functional simulation model with any Altera-supported VHDL or Verilog HDL simulator. This walkthourgh uses the ModelSim<sup>®</sup> Altera edition software to perform the simulation.

To set up RTL simulation in the Quartus II software using NativeLink®, follow these steps:

#### Get the Memory Simulation Model

1. Generate the IP functional simulation model.

You requested Verilog HDL models to be generated during the instantiate PHY and controller design flow step, described in "Step 2: Instantiate PHY and Controller in a Quartus II Project" on page 56. Figure 13 displays the results of your request.

The MegaWizard Plug-In Manager also generated a Verilog HDL testbench for the example design named ddr2\_foo\_example\_top\_tb.v, which is located in the testbench directory under the project directory.

Obtain and copy the memory model to a suitable location; for example, the testbench directory.

The Altera DDR2 SDRAM High-Performance Controller MegaCore automatically creates a generic memory model called <variation\_name>\_mem\_model.v

You can use Altera's generic memory model for functional simulation, or use the memory model provided by your memory vendor. If you choose to use Altera's generic model, directly proceed to step 10 in the "Setup Simulation Options in the Quartus II Software" on page 42.

For this example design, obtain the **ddr2.v** and **ddr2\_parameters.vh** memory model files from the *Micron* website and save them in the testbench directory.

#### Prepare the Simulation Model

Open the ddr2.v memory model file in a text editor, and add the following define statements to the top of the file:

```

`define sg3

`define x8

```

The two define statements prepare the DDR2 SDRAM memory model. The first statement specifies the memory device speed grade as -3. The second statement specifies the memory device width per DQS. This simulation uses the memory in the  $\times 8$  mode (instead of the  $\times 16$  mode).

- 4. Save the **ddr2.v** file.

- 5. Open the ddr2\_parameters.vh file, and search for the ADDR\_BITS parameter definition. You will find instances of this parameter, one for ×4, ×8, and ×16 bit wide interfaces. Change the ADDR\_BITS parameter for the ×8 interface from 14 to 13, since the example memory controller only uses 13 address bits.

```

'else 'ifdef x8

parameter ADDR BITS = 13; // MAX Address Bits

```

#### Instantiate the Memory Model in the Testbench

6. Open the **ddr2\_foo\_example\_top\_tb.v** testbench in a text editor.

The testbench instantiates the example design (ddr2\_foo\_example\_top) and a generic DDR2 SDRAM memory (ddr2\_foo\_mem\_model) module, and connects the memory interface signals appropriately. Before running the simulation, you need to edit the testbench to use the downloaded Micron memory model.

7. Locate and delete the following instance of the generic memory model in the testbench. Note that the START and END MEGAWIZARD comments must also be deleted to ensure the MegaWizard does not overwrite the changes when the controller megafunction is regenerated.

```

// <<START MEGAWIZARD INSERT MEMORY ARRAY

//This will need updating to match the memory models

//you are using.

//Instantiate a generated DDR memory model to match the

//datawidth and chipselect requirements

ddr2 foo mem model mem (

.mem dq (mem dq),

.mem dqs (mem dqs),

.mem addr (a delayed),

.mem ba (ba delayed),

.mem clk (clk to ram),

.mem clk n (clk to ram n),

.mem cke (cke delayed),

.mem ras n (ras n delayed),

.mem cas n (cas n delayed),

.mem we n (we n delayed),

.mem dm (dm delayed),

.mem odt (odt delayed)

);

// <<END MEGAWIZARD INSERT MEMORY ARRAY

```

Instantiate the first instance of the Micron ddr2 memory model as follows:

```

ddr2 memory_0(

.ck (clk to ram),

```

```

.ck_n (clk_to_ram_n),

.cke (cke_delayed),

.cs_n (cs_n_delayed),

.ras_n (ras_n_delayed),

.cas_n (cas_n_delayed),

.we_n (we_n_delayed),

.dm_rdqs (dm_delayed[0]),

.ba (ba_delayed),

.addr (a_delayed),

.dq (mem_dq[7:0]),

.dqs (mem_dqs[0]),

.dqs_n (),

.rdqs_n (),

.odt (odt_delayed),

```

Note the ports of the **ddr2** module are in lower-case. Since Verilog HDL is case sensitive, ensure that the port names use lower case. Also note that the **ddr2** module uses port names that are different from the generic Altera DDR2 model.

9. Similarly, create the other eight instances of the **ddr2** module. Note that the DQ, DQS, and DM bus indices are different for each instance. For example, the second ×8 memory instance should match the following:

```

ddr2 memory 1 (

.ck (clk to ram),

.ck n (clk to ram n),

.cke (cke delayed),

.cs n (cs n delayed),

.ras n (ras n delayed),

.cas n (cas n delayed),

.we n (we n delayed),

.dm rdqs (dm delayed[1]),

.ba (ba delayed),

.addr (a delayed),

.dq (mem dq[15:8]),

.dqs (mem dqs[1]),

.dqs n (),

.rdqs n (),

.odt (odt delayed),

);

```

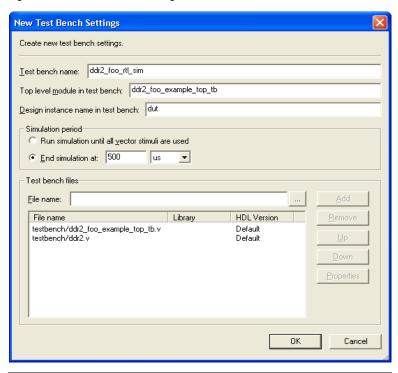

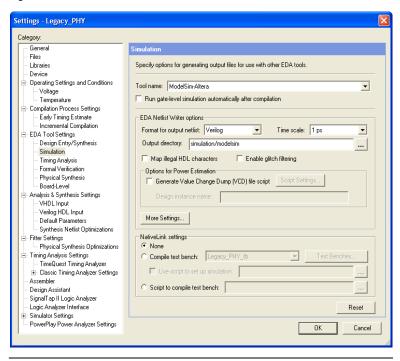

### Setup Simulation Options in the Quartus II Software

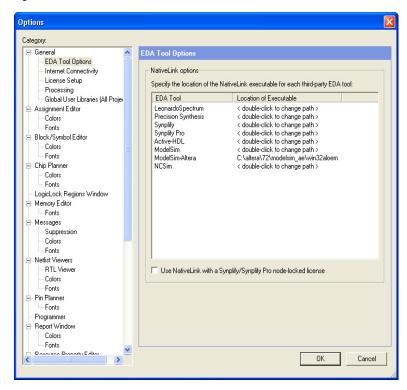

- 10. Save the modified testbench file. Check that the absolute path to your third-party simulator executable is set. On the Tools menu, click **Options.**

- Under the Category list, select EDA Tools Options, as shown in Figure 21. The default path is

C:\<version>\modelsim\_ae\win32aloem.

- 12. Click OK.

Figure 21. Set Path to ModelSim Altera Edition Software

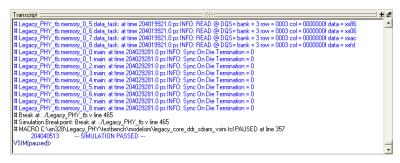

- 13. On the Assignments menu, point to **EDA Tool Settings** and select **Simulation**. The **EDA Tool Settings** panel appears.